DSP学习

DSP汇编指令

在DSP编程时经常会使用到一些汇编指令

我们可以在DSP2833x_Device.h当中找到它们的定义

1 |

| 汇编指令 | 作用 |

|---|---|

| EINT | 打开中断 |

| DINT | 关闭中断 |

| ERTM | 使能调试事件 |

| DRTM | 禁止调试事件 |

| EALLOW | 解禁处于禁写状态的寄存器 |

| EDIS | 重新恢复禁止写入状态 |

| ESTOP0 | 当仿真器连接时,若ESTOP0=1,则DSP运行到此处时停止运行;若不用仿真程序,则相当于NOP |

DSP外设

ADC

TMS320F28335拥有两个8通道的12位精度的ADC

内置的ADC有两个序列发生器,由2个独立的8通道模块组成

这两个模块既可以并联也可以级联

ADC只有一个转换器,所以只能做到同步采样,不能同步转换

下面简要介绍ADC的寄存器配置

- ADC模块控制寄存器1(ADCTRL1)

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15 | Reserved | 保留 |

| 14 | RESET | ADC模块软件复位 0:无效 1:复位整个ADC模块(复位后自动清零) |

| 13~12 | SUSMOD1 SUSMOD2 |

仿真悬挂模式 这两位决定产生仿真器挂起操作时执行的操作(如断点) 00:仿真挂起被忽略 01:当前排序完成后排序器与其他逻辑立即停止工作,锁存最终结果更新状态机 10:当前排序完成后排序器与其他逻辑立即停止工作,锁存最终结果更新状态机 11:仿真器挂起,排序器和其他逻辑立即停止 |

| 11~8 | ACQ_PS[3:0] | 采样时间选择位 控制SOC的脉冲宽度,同时也决定采样开关闭合的时间,SOC的脉冲宽度是ADCTRL[11~8] + 1个ADCLK周期数 |

| 7 | CPS | 转换时间预定标器 对外设时钟HSPCLK分频 0:f = CLK / 1 1:f = CLK / 2 CLK为定标之后的HSPCLK(ADCCLKPS[3:0]) |

| 6 | CONT_RUN | 运行方式 0:读取完转换序列后停止(启动/停止模式) 1:连续运行(从起始状态开始) |

| 5 | SEQ_OVER | 排序器运行方式 0:转换完MAX_CONVn个通道之后,排序器指针复位到初始状态 1:最后一个排序状态后,排序器指针复位到初始状态 |

| 4 | SEQ_CASC | 排序器模式 0:双排序器模式 1:级联排序器模式 |

| 3~0 | Reserved | 保留 |

- ADC模块控制寄存器2(ADCTRL2)

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15 | ePWM_SOCB_SEQ | 级联排序器使能ePWM_SOCB 0:无效 1:允许ePWM_SOCB触发 |

| 14 | RST_SEQ1 | 复位排序器 向该位写1立刻复位SEQ1为预触发状态,退出正在执行的转换序列 0:无效 1:复位排序器SEQ1到CONV00状态 |

| 13 | SOC_SEQ1 | SEQ1的启动转换触发 以下触发可引起该位的置位: 1. 软件向该位写1 2. ePWM_SOCA——ePWM触发 3. ePWM_SOCB——ePWM触发(仅在级联模式中) 4. 外部引脚 当触发源到来时,有3种情况 1. SEQ空闲且SOC位清零,SEQ1立即开始,允许任何触发“挂起”的请求 2. SEQ1忙且SOC位清零,SEQ1立即开始,此时表示可以挂起一个触发请求,当完成当前转换,SEQ1重新开始时,该位清零 3. SEQ1忙且SOC位置位,此时任何触发都会忽视 |

| 12 | Reserved | 保留 |

| 11 | INT_ENA_SEQ1 | SEQ1中断使能 使能INT SEQ1向CPU发出中断申请 0:禁止发出中断申请 1:允许发出中断申请 |

| 10 | INT_MOD_SEQ1 | SEQ1中断模式 0:每个SEQ1序列结束时,INT SEQ1置位 1:每隔一个SEQ1序列结束时,INT SEQ1置位 |

| 9 | Reserved | 保留 |

| 8 | ePWM_SOCA_SEQ1 | SEQ1的ePWM的SOCA屏蔽位 0:ePWM的触发信号不能启动SEQ1 1:ePWM的触发信号可以启动SEQ1 |

| 7 | EXT_SOC_SEQ1 | SEQ1的外部信号启动位 0:无操作 1:外部ADCSOC引脚信号启动ADC自动转换序列 |

| 6 | RST_SEQ2 | 复位SEQ2 0:无操作 1:立即复位SEQ2为预触发状态,退出正在执行的转换序列 |

| 5 | SOC_SEQ2 | SEQ2的启动转换触发 仅适用于双排序模式,在级联模式下不使用 以下触发可引起该位的置位: 1. 软件向该位写1 2. ePWM_SOCA——ePWM触发 当触发源到来时,有3种情况 1. SEQ2空闲且SOC位清零,SEQ2立即开始,允许任何触发“挂起”的请求 2. SEQ2忙且SOC位清零,SEQ2立即开始,此时表示可以挂起一个触发请求,当完成当前转换,SEQ2重新开始时,该位清零 3. SEQ2忙且SOC位置位,此时任何触发都会忽视 |

| 4 | Reserved | 保留 |

| 3 | INT_ENA_SEQ2 | SEQ2中断使能 使能INT SEQ2向CPU发出中断申请 0:禁止发出中断申请 1:允许发出中断申请 |

| 2 | INT_MOD_SEQ2 | SEQ2中断模式 0:每个SEQ2序列结束时,INT SEQ2置位 1:每隔一个SEQ2序列结束时,INT SEQ2置位 |

| 1 | Reserved | 保留 |

| 0 | ePWM_SOCB_SEQ2 | SEQ2的ePWM的SOCA屏蔽位 0:ePWM的触发信号不能启动SEQ2 1:ePWM的触发信号可以启动SEQ2 |

- ADC模块控制寄存器(ADCTRL3)

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15~8 | Reserved | 保留 |

| 7~6 | ADCBGRFDN[1:0] | ADC带隙和参考的电源控制 0:带隙与参考电路掉电 1:带隙与参考电路上电 |

| 5 | ADCPWDN | ADC电源控制 0:除带隙与参考电路外的ADC其他模拟电路掉电 1:除带隙与参考电路外的ADC其他模拟电路上电 |

| 4~1 | ADCCLKPS[3:0] | ADC的内核时钟分频器 |

| 0 | SMODE_SEL | 采样模式选择 0:顺序采样 1:同步采样 |

- 最大转换通道数(ADCMAXCONV)

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15~7 | Reserved | 保留 |

| 6~0 | MAXCONVn | MAX CONVn定义了自动转换中最多转换的通道数 对于SEQ1,使用MAXCONV1[2:0] 对于SEQ2,使用MAXCONV2[2:0] 对于SEQ,使用MAXCONV1[3:0] |

- 自动排序状态寄存器(ADCASEQSR)

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15~12 | Reserved | 保留 |

| 11~8 | SEQ_CNTR | 排序器计数器状态位 转换通道数为SEQ_CNTR + 1 |

| 7 | Reserved | 保留 |

| 6~0 | SEQ_STATE | 保留用作Ti测试 |

- ADC状态和标志寄存器

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15~8 | Reserved | 保留 |

| 7 | EOS_BUF2 | SEQ2的排序缓冲结束位 |

| 6 | EOS_BUF1 | SEQ1的排序缓冲结束位 |

| 5 | NI_SEQ2_CLR | 中断清除位 0:无影响 1:清除SEQ2的中断标志位 |

| 4 | NI_SEQ1_CLR | 中断清除位 0:无影响 1:清除SEQ1的中断标志位 |

| 3 | SEQ2_BSY | SEQ2忙状态位 0:空闲 1:忙 |

| 2 | SEQ1_BSY | SEQ1忙状态位 0:空闲 1:忙 |

| 1 | INT_SEQ2 | SEQ2中断标志位 0:没有中断事件 1:已产生中断事件 |

| 0 | INT_SEQ1 | SEQ1中断标志位 0:没有中断事件 1:已产生中断事件 |

- ADC输入通道选择排序控制寄存器

| ADCCHSELSEQ1 | ADCCHSELSEQ1 | ADCCHSELSEQ1 | ADCCHSELSEQ1 |

|---|---|---|---|

| 15~12 | 11~8 | 7~4 | 3~0 |

| CONV03 | CONV02 | CONV01 | CONV00 |

| ADCCHSELSEQ2 | ADCCHSELSEQ2 | ADCCHSELSEQ2 | ADCCHSELSEQ2 |

|---|---|---|---|

| 15~12 | 11~8 | 7~4 | 3~0 |

| CONV07 | CONV06 | CONV05 | CONV04 |

| ADCCHSELSEQ3 | ADCCHSELSEQ3 | ADCCHSELSEQ3 | ADCCHSELSEQ3 |

|---|---|---|---|

| 15~12 | 11~8 | 7~4 | 3~0 |

| CONV11 | CONV10 | CONV09 | CONV08 |

| ADCCHSELSEQ4 | ADCCHSELSEQ4 | ADCCHSELSEQ4 | ADCCHSELSEQ4 |

|---|---|---|---|

| 15~12 | 11~8 | 7~4 | 3~0 |

| CONV15 | CONV14 | CONV13 | CONV12 |

CONVxx可以为一次自动排序转换选定16个ADC输入通道中的一个通道

| CONVxx | ADC输入通道选择 | CONVxx | ADC输入通道选择 |

|---|---|---|---|

| 0000 | ADCINA0 | 1000 | ADCINB0 |

| 0001 | ADCINA1 | 1001 | ADCINB1 |

| 0010 | ADCINA2 | 1010 | ADCINB2 |

| 0011 | ADCINA3 | 1011 | ADCINB3 |

| 0100 | ADCINA4 | 1100 | ADCINB4 |

| 0101 | ADCINA5 | 1101 | ADCINB5 |

| 0110 | ADCINA6 | 1110 | ADCINB6 |

| 0111 | ADCINA7 | 1111 | ADCINB7 |

- 结果寄存器(ADCRESULTn)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | X | X | X | X |

F28335的内部ADC只有12位,所以有4位是空着的

这也是为什么每次在获取ADC数据的时候数据要右移4位了

GPIO

F28335的GPIO有一个比较特殊的特性:可以使能限制选择器

即当输入信号在一定时间内保持不变才会被认为是有效信号,否则保持原来的状态不变

下面是GPIO的相关寄存器

| 名称 | 地址 | 空间地址 | 描述 |

|---|---|---|---|

| GPACTRL | 0X6F80 | 2 | GPIOA控制寄存器 |

| GPAQSEL1 | 0X6F82 | 2 | GPIOA量化控制寄存器1 |

| GPAQSEL2 | 0X6F84 | 2 | GPIOA量化控制寄存器2 |

| GPAMUX1 | 0X6F86 | 2 | GPIOA选择寄存器1 |

| GPAMUX2 | 0X6F88 | 2 | GPIOA选择寄存器2 |

| GPIOADIR | 0X6F8A | 2 | GPIOA方向寄存器 |

| GPIOAPUD | 0X6F8C | 2 | GPIOA上拉禁止寄存器 |

| GPBCTRL | 0X6F90 | 2 | GPIOB控制寄存器 |

| GPBQSEL1 | 0X6F92 | 2 | GPIOB量化控制寄存器1 |

| GPBQSEL2 | 0X6F94 | 2 | GPIOB量化控制寄存器2 |

| GPBMUX1 | 0X6F96 | 2 | GPIOB选择寄存器1 |

| GPBMUX2 | 0X6F98 | 2 | GPIOB选择寄存器2 |

| GPIOBDIR | 0X6F9A | 2 | GPIOB方向寄存器 |

| GPIOBPUD | 0X6F9C | 2 | GPIOB上拉禁止寄存器 |

| GPCMUX1 | 0X6FA6 | 2 | GPIOC选择寄存器1 |

| GPCMUX2 | 0X6FA8 | 2 | GPIOC选择寄存器2 |

| GPCDIR | 0X6FAA | 2 | GPIOC方向寄存器 |

| GPCPUD | 0X6FAC | 2 | GPIOC上拉禁止寄存器 |

| GPIOXINT1SEL | 0X6FE0 | 1 | 外部中断源选择寄存器1 |

| GPIOXINT2SEL | 0X6FE1 | 1 | 外部中断源选择寄存器2 |

| GPIONMISEL | 0X6FE2 | 1 | 不可屏蔽中断源选择寄存器 |

| GPIOXINT3SEL | 0X6FE3 | 1 | 外部中断源选择寄存器3 |

| GPIOXINT4SEL | 0X6FE4 | 1 | 外部中断源选择寄存器4 |

| GPIOXINT5SEL | 0X6FE5 | 1 | 外部中断源选择寄存器5 |

| GPIOXINT6SEL | 0X6FE6 | 1 | 外部中断源选择寄存器6 |

| GPIOXINT7SEL | 0X6FE7 | 1 | 外部中断源选择寄存器7 |

| GPIOLPMSEL | 0X6FE8 | 1 | 唤醒低功耗模式源选择器 |

下面介绍几个比较常用的GPIO的寄存器

- GPACTRL寄存器

| 位 | 字段 | 功能描述 |

|---|---|---|

| 31~24 | QUALPRD3 | GPIO24~GPIO31引脚特定的采样周期 0x00:采样周期 = 系统时钟 0x01:采样周期 = 2 x 系统时钟 0xFF:采样周期 = 510 x 系统时钟 |

| 23~16 | QUALPRD2 | GPIO16~GPIO23引脚特定的采样周期 具体配置同上 |

| 15~8 | QUALPRD1 | GPIO8~GPIO15引脚特定的采样周期 具体配置同上 |

| 7~0 | QUALPRD0 | GPIO0~GPIO7引脚特定的采样周期 具体配置同上 |

GPBCTRL 的配置与 GPACTRL 类似, 只是配置下边的 32 个 IO 口而已

- GPAQSEL寄存器

GPAQSEL1 寄存器用来配置采样数,也可以认为是滤波数,当干扰信号持续采样周期小于该寄存器设置的采样周期数时,干扰信号被滤除

| 位 | 字段 | 功能描述 |

|---|---|---|

| 31~0 | GPIO15~GPIO0 | 对GPIO0~GPIO15选择输入限制 00:仅与系统时钟同步,引脚配置为外设与GPIO都有效 01:采用3个采样周期宽度限制,引脚配置为外设或GPIO有效 10:采用6个采样周期宽度限制,引脚配置为外设或GPIO有效 11:不同步/不限制(仅应用于配置为外设的引脚,如果配置为GPIO,则该选项与00相同) |

- GPxDIR寄存器

GPxDIR 寄存器用来配置 GPIO 的输入输出方向

| 位 | 字段 | 功能描述 |

|---|---|---|

| 31~0 | GPIO31~GPIO0 | 0:(默认)GPIO输入 1:GPIO输出 |

TIM

TMSF28335有三个Timer,其中TIM2是为操作系统DSP/BIOS保留的,当未移植操作系统时,可以当作普通定时器使用

这三个定时器的中断信号分别为TINT0,TINT1,TINT2,分别对应于中断向量INT1,INT13,INT14

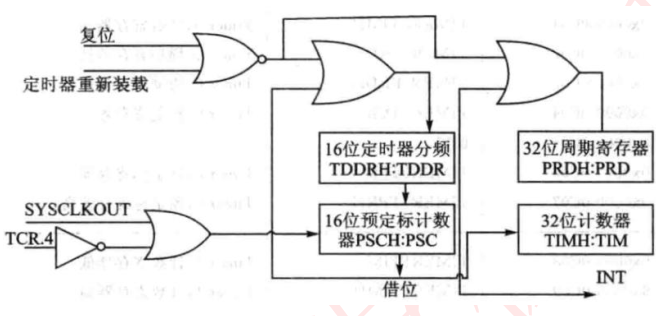

定时器的功能如下图所示

当系统时钟(SYSCLKOUT) 来一个脉冲,PSCH:PSC预定标计数器减1,当PSCH:PSC 预定标计数器减到0的时候,预定标计数器产生下溢后向定时器的 32 位计数器TIMH:TIM借位, 即TIMH:TIM计数器减1,同时PSCH:PSC可以重载定时器分频寄存器(TDDRHTDDR)的值;当计数寄存器TIMH: TIM减到0产生下溢的时候,计数寄存器会重载周期寄存器(PRDH:PRD)的值,同时定时器会产生一个中断信号给CPU

定时器中断属于PIE中断,中断信号经过PIE后,再进入处理器,定时器0的中断属于PIE第一组中断中的第7个小中断

下面是定时器相关寄存器

| 地址 | 寄存器 | 名称 |

|---|---|---|

| 0x0000 0C00 | TIMER0TIM | Timer0,计数寄存器低位 |

| 0x0000 0C01 | TIMER0TIMH | Timer0,计数寄存器高位 |

| 0x0000 0C02 | TIMER0PRD | Timer0,周期寄存器低位 |

| 0x0000 0C03 | TIMER0PRDH | Timer0,周期寄存器高位 |

| 0x0000 0C04 | TIMER0TCR | Timer0,控制寄存器 |

| 0x0000 0C05 | 保留 | 保留 |

| 0x0000 0C06 | TIMER0TPR | Timer0,预定标寄存器低位 |

| 0x0000 0C07 | TIMER0TPRH | Timer0,预定标寄存器高位 |

| 0x0000 0C08 | TIMER1TIM | Timer1,计数寄存器低位 |

| 0x0000 0C09 | TIMER1TIMH | Timer1,计数寄存器高位 |

| 0x0000 0C0A | TIMER1PRD | Timer1,周期寄存器低位 |

| 0x0000 0C0B | TIMER1PRDH | Timer1,周期寄存器高位 |

| 0x0000 0C0C | TIMER1TCR | Timer1,控制寄存器 |

| 0x0000 0C0D | 保留 | 保留 |

| 0x0000 0C0E | TIMER1TPR | Timer1,预定标寄存器低位 |

| 0x0000 0C0F | TIMER1TPRH | Timer1,预定标寄存器高位 |

| 0x0000 0C10 | TIMER2TIM | Timer2,计数寄存器低位 |

| 0x0000 0C11 | TIMER2TIMH | Timer2,计数寄存器高位 |

| 0x0000 0C12 | TIMER2PRD | Timer2,周期寄存器低位 |

| 0x0000 0C13 | TIMER2PRDH | Timer2,周期寄存器高位 |

| 0x0000 0C14 | TIMER2TCR | Timer2,控制寄存器 |

| 0x0000 0C15 | 保留 | 保留 |

| 0x0000 0C16 | TIMER2TPR | Timer2,预定标寄存器低位 |

| 0x0000 0C17 | TIMER2TPRH | Timer2,预定标寄存器高位 |

- 定时器控制寄存器TIMERxTCR

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15 | TIF | CPU定时器中断标志位 当定时计数器递减至0时将该位置1,可以清零 0:无影响 1:写1清零 |

| 14 | TIE | 定时器中断使能 当定时计数器递减至0时,若该位使能,则定时器向CPU申请中断 |

| 13,12 | 保留 | 保留 |

| 11 | FREE | CPU定时器仿真模式 |

| 10 | SOFT | CPU定时器仿真模式 FREE SOFT 0 0 下次计数器递减操作完成后定时器停止 0 1 计数器递减到0后定时器停止 其他情况:自由运行 |

| 9~6 | 保留 | 保留 |

| 5 | TRB | 定时器重载控制位 0:禁止重载 1:使能重载 |

| 4 | TSS | 启动和停止定时器的状态位 0:为了启动或者重新启动,将其清零 1:置1停止定时器 |

| 3~0 | 保留 | 保留 |

- 定时器预定标寄存器

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15~8 | PSC | 定时器预定标计数器 PSC保存当前定时器的预定标的值,当PSCH:PSC大于0时,每个定时器源时钟周期PSCH:PSC递减1,当PSCH:PSC递减至0时,即一个定时器周期 PSCH:PSC使用TDDRH:TDDR内的值重新装载,定时器计数寄存器减1,只要软件将定时器的重新装载位置1,PSCH:PSC也会重新装载,可以读取PSCH:PSC内的值,但是不能直接写这些位,必须从TDDRH:TDDR获取要装载的值,复位时PSCH:PSC清零 |

| 7~0 | TDDR | 定时器分频寄存器 每隔(TDDRH:TDDR + 1)个定时器源时钟周期,定时器计数寄存器(TIMH:TIM)减1,复位时TDDRH:TDDR清零 当PSCH:PSC等于0时,一个定时器源时钟周期后,重新将TDDRH:TDDR的内容装载到PSCH:PSC,TIMH:TIM减1 当软件将定时器的重新装载位(TRB)置1时,PSCH:PSC也会重新装载 |

- 定时器计数器

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15~0 | TIM | TIM寄存器保存当前32位定时器计数值的低16位,每隔(TDDRH:TDDR + 1)个时钟周期,TIMH:TIM减1 当TIMH:TIM递减到0时,TIMH:TIM寄存器重新装载PRDH:PRD寄存器保存的周期值,并产生定时器中断TINT信号 |

- 定时器周期寄存器

| 位 | 名称 | 功能描述 |

|---|---|---|

| 15~0 | PRD | PRD寄存器保存32位周期值的低16位,PRDH保存高16位 当TIMH:TIM递减到0时,在下次定时周期开始之前TIMH:TIM寄存器重新装载PRDH:PRD寄存器保存的周期值 当用户将定时器控制寄存器(TCR)的定时器重新装载位(TRB)置位时,TIMH:TIM也会重新装载PRDH:PRD寄存器保存的周期值 |

DSP写起来真的是麻,幸好项目做完了,这个教程差不多就这样咕咕了吧()

To be continued